# Low Power Consumption Complementary Inverters with n-MoS<sub>2</sub> and p-WSe<sub>2</sub> Dichalcogenide Nanosheets on Glass for Logic and Light-**Emitting Diode Circuits**

Pyo Jin Jeon, Jin Sung Kim, June Yeong Lim, Youngsuk Cho, Atiye Pezeshki, Hee Sung Lee, Sanghyuck Yu, Sung-Wook Min, and Seongil Im\*

Institute of Physics and Applied Physics, Yonsei University, 50 Yonsei-ro, Seodaemun-gu, Seoul 120-749, Korea

Supporting Information

ABSTRACT: Two-dimensional (2D) semiconductor materials with discrete bandgap become important because of their interesting physical properties and potentials toward future nanoscale electronics. Many 2D-based field effect transistors (FETs) have thus been reported. Several attempts to fabricate 2D complementary (CMOS) logic inverters have been made too. However, those CMOS devices seldom showed the most important advantage of typical CMOS: low power consumption. Here, we adopted p-WSe<sub>2</sub> and n-MoS<sub>2</sub> nanosheets separately for the channels of bottom-gate-patterned FETs, to fabricate 2D dichalcogenide-based hetero-CMOS inverters on the same glass substrate. Our hetero-CMOS inverters with electrically isolated FETs demonstrate novel and superior device performances of a maximum voltage gain as ~27, sub-nanowatt power consumption, almost ideal noise margin approaching  $0.5V_{\rm DD}$  (supply voltage,  $V_{\rm DD}$  = 5 V) with a transition voltage of 2.3 V, and ~800 µs for switching delay. Moreover, our glass-substrate CMOS device nicely performed digital logic (NOT, OR, and AND) and push-pull circuits for organic light-emitting diode switching, directly displaying the prospective of practical applications.

## **■ INTRODUCTION**

After graphene, 1,2 two-dimensional (2D) semiconductor materials with discrete bandgap have attracted much attention from many researchers, owing to their interesting physical properties and potentials for future nanoscale electronics. 3-35 Like graphene, those 2D semiconductors are formed by mechanical exfoliation using scotch tapes in general, so that those are called nanosheet or nanoflake. Among many nanosheet materials, molybdenum disulfide (MoS<sub>2</sub>)<sup>9-24</sup> and tungsten diselenide  $(WSe_2)^{23-35}$  are known as pacesetting materials, because they have displayed excellent carrier mobility, high on/off current ratio, and good sub-threshold swing in a field-effect transistor (FET) form as 2D n- and ptype channels, respectively. In fact, 2D WSe2 has been found ambipolar, so that researchers might even report complementary-like inverters<sup>26,27</sup> using such ambipolar properties; this WSe<sub>2</sub> played as both n- and p-channel depending upon the contact metal, <sup>25-34</sup> chemical doping in the channel, <sup>27-29</sup> and the polarity of applied gate voltages. 30-34 However, the homogeneous 2D WSe2 complementary inverter with chemical doping<sup>27</sup> shows relatively unstable behavior in air ambience,

because the chemical doping for n-type activity could not be supportive for ambient stability. It means that the n-type doping is difficult and probably not matched to the nature of exfoliated 2D WSe2, which is slightly closer to p-type than to ntype. Another type of homogeneous complementary inverter, comprised of dual-gate WSe<sub>2</sub> FETs, <sup>26</sup> always required additional gate biases to adjust channel polarities and threshold voltages. Therefore, many researchers have rather attempted to fabricate homogeneous 2D inverters of depletion-load type<sup>7–11</sup> than complementary inverters, although depletion-load inverters should be inferior to the complementary inverter with respect to power dissipation and voltage gain. Recently, several efforts to fabricate stable heterogeneous complementary-like (hetero-CMOS) inverters with two different channel materials, among which one-dimensional (1D)-2D hybrid channels 15,35 and 2D-2D heterogeneous dichalcogenide channels<sup>21-23</sup> are found. However, until now, such 2D-2D dichalcogene-based

Received: July 6, 2015 Accepted: September 24, 2015 Published: September 24, 2015

KEYWORDS: complementary inverter, MoS2 WSe2 glass, sub-nanowatt, high gain

CMOS inverters, which would be the most natural in device form, are still a few and display so primitive performances without reporting such important basics as power consumption and dynamic switching. In particular, we may hardly find any power consumption data yet from 2D-2D CMOS reports (see details in Table S1), although low power consumption is the most important advantage of the CMOS inverter over single-FET-type inverters.

Here, we adopted WSe<sub>2</sub> and MoS<sub>2</sub> nanosheets for separate pand n-channels using a direct imprint method, 15-18,24 to fabricate 2D dichalcogenide-based hetero-CMOS inverters not only on SiO<sub>2</sub>/p<sup>+</sup>-Si but also on a glass substrate. Our hetero-CMOS inverters with bottom-gated p- and n-FETs well operate particularly on a glass substrate, demonstrating novel and superior device performances of a maximum voltage gain as ~27, sub-nanowatt power consumption in switching, almost ideal noise margin approaching  $0.5 V_{\mathrm{DD}}$  (supply voltage,  $V_{\mathrm{DD}}$  = 5 V) with a transition voltage of 2.3 V, and  $\sim$ 800  $\mu$ s for switching time. Likewise, satisfying most of the important CMOS properties, our glass-substrate CMOS device performed digital logic (NOT, OR, and AND) and push-pull circuits for organic light-emitting diode (OLED) switching.

#### **EXPERIMENTAL SECTION**

Device Fabrication. First of all, two kinds of gate dielectrics were prepared: (i) thermal oxidized 285 nm thick SiO<sub>2</sub> on heavily doped p<sup>+</sup>-Si wafer as the universal gate and (ii) atomic-layer deposited (ALD) 50 nm thick Al<sub>2</sub>O<sub>3</sub> on a gate-patterned 25/25 nm thick Au/Ti bilayer electrode (Ti was always deposited prior to Au as a result of its better adhesion to glass). As the next step, a direct imprint method<sup>15</sup> was implemented, as described in panels a-e of Figure S1, to transfer two different kinds of nanosheets on target places. A MoS2 nanosheet was mechanically exfoliated using a sticky polydimethylsiloxane (PDMS) stamp from single-crystal bulk MoS<sub>2</sub> (see Figure S1a). The PDMS stamp with exfoliated MoS<sub>2</sub> was transferred onto a quartz plate, and the quartz plate with our MoS2 nanosheet was flipped over and moved to be aligned on previously prepared two kinds of substrates that had already been mounted on the stage of a charge-coupled device (CCD)-equipped microaligner, as shown in Figure S1b. The MoS2 nanosheet was then precisely attached on a gate dielectric by controlling the motion of the microaligner stage for van der Waals force, being monitored by the CCD image. Figure S1c illustrates the MoS<sub>2</sub> nanosheet stacked on SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> gate dielectrics by van der Waals force. A 25/25 nm thick Au/Ti electrode was patterned for ohmic source/drain (S/D) contact with a n-channel MoS<sub>2</sub> nanosheet (Ti was always deposited prior to Au as a result of its work function matching with MoS<sub>2</sub>).<sup>17</sup> The same attachment processes were carried out to transfer and attach the WSe2 nanoshseet close to the MoS2 nanosheet FET (see Figure S1d). Sequentially, 50 nm thick Pt electrode, which is known to have a ~5.5 eV work function, was patterned to make low-resistance contact with a p-channel WSe<sub>2</sub> nanosheet, as shown in Figure S1e. Both the metal electrodes of Au/Ti and Pt were patterned by photolithography and lift-off method and were deposited by a direct current (DC) magnetron sputtering system in a high-vacuum chamber of  $\sim 10^{-7}$  Torr. After completion of electrical measurements of the unencapsulated complementary inverter, 200 nm thick fluoropolymer CYTOP (Asahi glass, CTX-809M) was stacked by the spin-coating method on top, followed by curing at 100 °C for 30 min.

For the push-pull circuit operation, the output terminal of CYTOP-encapsulated complementary inverter was interconnected by Au wiring with two antiparallel green ( $\lambda \sim 560$  nm) OLEDs (respective light-emitting area of 2 × 2 mm<sup>2</sup>), which were manufactured from Samsung Display.

Electrical Measurements. All electrical measurements were performed in the dark with a semiconductor parameter analyzer (Agilent 4155C) and function generator (Tektronix AFG3022B).

## RESULTS AND DISCUSSION

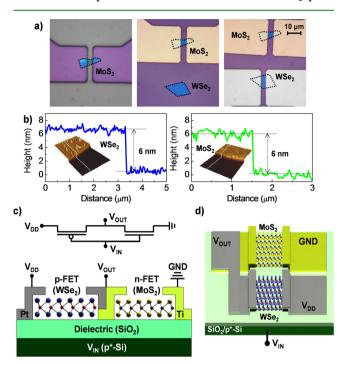

Hetero-CMOS on SiO<sub>2</sub>/p<sup>+</sup>-Si. Figure 1a displays the hetero-CMOS processes on a 285 nm thick SiO<sub>2</sub>/p<sup>+</sup>-Si

Figure 1. (a) Optical microscopic images displaying device fabrication processes, which were implemented on a 285 nm thick SiO<sub>2</sub>/p<sup>+</sup>-Si wafer using the direct imprint method. The left image indicates a MoS<sub>2</sub> nanosheet along with ultraviolet (UV)-patterned photoresist prior to Au/Ti S/D deposition, while the central image shows a fabricated n-MoS<sub>2</sub> FET and a direct imprint-transferred WSe<sub>2</sub>. The right image displays fabrication-completed n- and p-FETs. (b) Line profiles and topographic images of (left) WSe2 and (right) MoS2 nanosheets as obtained from AFM. (c and d) Schematic circuit diagram, crosssection, and 3D image illustrating the hetero-CMOS inverter on a 285 nm thick SiO<sub>2</sub>/p<sup>+</sup>-Si universal gate.

universal gate. After finding a 6-7 nm thin exfoliated MoS<sub>2</sub>, an Au/Ti S/D electrode was patterned by photolithography and lift-off processes. Then, a WSe2 nanosheet of about the same thickness was transferred near a MoS2 sheet by the direct imprinting method, <sup>15–18,24</sup> followed by Pt electrode patterning for S/D contact [see the atomic force microscopy (AFM) results in Figure 1b for the respective thickness profiles and images of MoS2 and WSe2]. These two FETs are connected in series to function as a CMOS inverter couple, as shown in the schematic cross-section and three-dimensional (3D) views of panels c and d of Figure 1.

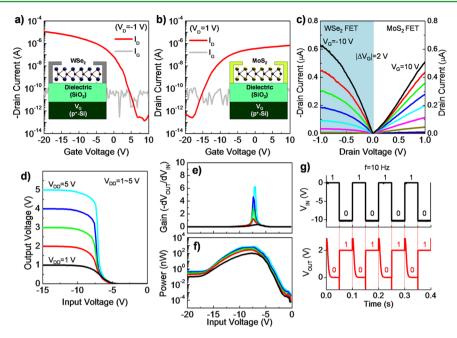

Electrical Performances of Hetero-CMOS on SiO<sub>2</sub>/p<sup>+</sup>-Si. The electrical properties of our individual 2D FET with p-WSe<sub>2</sub> and n-MoS<sub>2</sub> channels on the universal gate are introduced in panels a and b of Figure 2. According to the transfer curves (drain current-gate voltage,  $I_D$ - $V_{GS}$ ) of p- and n-FETs, 2D WSe<sub>2</sub> FET shows an order of magnitude higher oncurrent than that of MoS<sub>2</sub> FET, also displaying more desirable behavior with respect to the threshold voltage ( $V_{\rm TH} = -10~{\rm V}$ for n-FET and +1 V for p-FET, as shown in panels d and e of Figure S2). Therefore, our bottom-gate FET architecture apparently operates better for WSe2 than MoS2 nanosheet, promising a higher mobility from p-FET. Output curves (drain current-drain voltage,  $I_{\rm D}$ - $V_{\rm DS}$ ) of FETs display in Figure 2c

Figure 2. Drain current—gate voltage  $(I_{\rm D}-V_{\rm GS})$  transfer curves of universal gate FETs using (a) p-channel WSe<sub>2</sub> and (b) n-channel MoS<sub>2</sub> nanosheets as obtained from  $|V_{\rm DS}|=1$  V (see the respective insets for schematic cross-sections of p- and n-FETs). (c) Drain current—drain voltage  $(I_{\rm D}-V_{\rm DS})$  output curves of universal gate FETs using p-channel WSe<sub>2</sub> and n-channel MoS<sub>2</sub> nanosheets in a gate voltage range of  $V_{\rm GS}$  from -10 to 10 V with 2 V steps. (d) Voltage transfer characteristics  $(V_{\rm IN}-V_{\rm OUT})$ , (e) voltage gains  $(-dV_{\rm OUT}/dV_{\rm IN})$ , and (f) power consumptions  $(P=I_{\rm DD}V_{\rm DD})$  of hetero-CMOS on the wafer substrate as obtained under various supply voltages  $(V_{\rm DD})$  values) ranging from 1 to 5 V. (g) Dynamic output voltage response obtained from square wave input of 0 and -10 V at 10 Hz under  $V_{\rm DD}=2$  V.

that Au/Ti and Pt electrodes are working well for ohmic contacts to n- and p-channels, respectively. Interestingly, the output curves of p-FET show quite a saturation behavior, while those of n-FET display linear behavior. This means that the p-FET with 2D WSe<sub>2</sub> tends to readily saturate unlike the n-FET with the similarly thin MoS<sub>2</sub>. We attribute this behavior to any unique materials characteristic of 2D WSe<sub>2</sub>. The saturation mobility ( $\mu_{\rm sat}$ ) of p-FET was estimated to be ~4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (linear mobility,  $\mu_{\rm lin}$  ~ 100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), and n-FET shows only ~1.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for its linear mobility ( $\mu_{\rm lin}$ ) (see the respective plots of panels a—c of Figure S2), when we used two different mobility eqs 1 and 2 shown below.<sup>36</sup>

$$\mu_{\rm sat} = \frac{2}{C_{\rm OX}} \frac{L}{W} \left( \frac{\partial \sqrt{I_{\rm D}}}{\partial V_{\rm GS}} \right)^2 \qquad \text{for saturation mobility}$$

(1)

$$\mu_{\rm lin} = \frac{1}{V_{\rm D}C_{\rm OX}} \frac{L}{W} \frac{\partial I_{\rm D}}{\partial V_{\rm GS}} \qquad \text{for linear mobility}$$

(2)

CMOS inverter circuit on the universal gate resulted in the voltage transfer characteristics (VTCs) of Figure 2d, which was obtained under various supply voltages ( $V_{\rm DD}$  values) ranging from 1 to 5 V. Because our n-MoS $_2$  FET was in quite a depletion mode, our hetero-CMOS inverter displays a very negative transition voltage at -7.5 V, along with a maximum voltage gain ( $-{\rm d}V_{\rm OUT}/{\rm d}V_{\rm IN}$ ) of  $\sim$ 6 in Figure 2e. Moreover, this device shows a broad range of peak power consumption ( $P=V_{\rm DD}I_{\rm DD}$ ) during high—low switching (Figure 2f), which originates from unpatterned gate structure (Figure 1c). The peak power consumption appears as large as  $\sim$ 1  $\mu$ W. Dynamic inverter switching using 0 and -10 V input ( $V_{\rm IN}$ ) was demonstrated at 10 Hz under  $V_{\rm DD}$  of 2 V in Figure 2g, but it began to show over-/undershoot of output voltage ( $V_{\rm OUT}$ ) at

10 Hz (along with 10 ms delay) as a result of overlap capacitance-induced booster effects. <sup>24,37,38</sup>

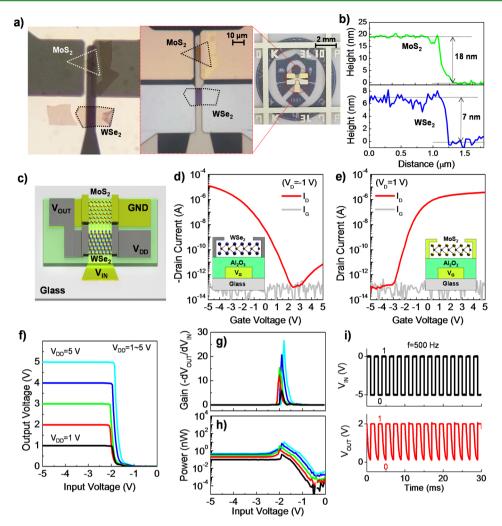

Electrical Performances of Hetero-CMOS on Glass. To remove such undesirable effects from an unpatterned universal gate as large power consumption, low voltage gain, and switching speed limit along with  $V_{\rm OUT}$  overshoot,  $^{24,37,38}_{}$  we fabricated a patterned bottom-gate hetero-CMOS inverter on a glass substrate. Figure 3a shows our hetero-CMOS inverter fabrication processes on glass, which was basically the same as those on the  $SiO_2/p^+$ -Si substrate, except the gate metal (Au/ Ti) was patterned on glass prior to atomic layer deposition (ALD) of 50 nm thick Al<sub>2</sub>O<sub>3</sub> dielectric. As shown in the central photo image zoomed from our CMOS device on glass, there is still a little gate/source overlap area in our FETs and the central device image is schematically described in Figure 3c. In this hetero-CMOS couple with two FETs, the MoS<sub>2</sub> thickness was 3 times larger than that of WSe<sub>2</sub> ( $\sim$ 7 nm) (Figure 3b). According to the transfer curves of p- and n-FETs on glass (panels d and e of Figure 3, respectively), a few times higher on-current  $I_D$  is achieved from p-FET with 2D WSe<sub>2</sub> approaching 10  $\mu$ A at -5V of gate bias. Both FETs show negative threshold voltages of -1.3 V for p-FET and -1 V for n-FET (see the respective plots of panels f and g of Figure S3). Field effect mobilities were estimated on the basis of the transfer curves but also the output curves of the two FETs in panels a and b of Figure S3. Although the output curves of p-FET somewhat contain saturation behavior, we calculated both of its linear (~16 cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup>) and saturation ( $\sim$ 7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) mobilities. The linear mobility is  $\sim 10$  times higher than that of n-FET (1.6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) according to the respective plots of panels c-e of Figure S3. The gate leakage current from both p- and n-FETs on glass displayed a much desirable level of ~100 fA, which is 3 orders of magnitude lower than that from FETs on wafer ( $\sim$ 100 pA). It is because the gate-patterned CMOS on glass has a much

Figure 3. (a) Left optical image was taken under bottom illumination through glass during the fabrication process, indicating the patterned bottom-gate, completed  $MoS_2$  FET and transferred  $WSe_2$  flake. The central image indicates a completed hetero-CMOS inverter as another optical image taken using top illumination, while the right image is a snapshot photo image of hetero-CMOS on glass. (b) AFM line profiles of 18 nm thick  $MoS_2$  and 7 nm thin  $WSe_2$  nanosheets. (c) Schematic 3D illustration of hetero-CMOS inverter with a 50 nm thick  $Al_2O_3$  gate.  $I_D-V_{GS}$  transfer curves of patterned bottom-gate FETs for (d) p-channel  $WSe_2$  FET and (e) n-channel  $MoS_2$  FET as obtained from  $|V_{DS}| = 1$  V (the respective insets show schematic cross-sections of p- and n-FETs). (f) Voltage transfer characteristics  $(V_{IN}-V_{OUT})$ , (g) voltage gains  $(-dV_{OUT}/dV_{IN})$ , and (h) power consumptions  $(I_{DD}V_{DD})$  of hetero-CMOS on a glass substrate were obtained under various supply voltages  $(V_{DD})$  values) ranging from 1 to 5 V. (i) Dynamic output voltage responses obtained from square wave input of 0 and -5 V at 500 Hz frequencies under  $V_{DD} = 2$  V.

smaller overlap area between gate/source electrodes. The hetero-CMOS inverter with a patterned gate on glass (see Figure 3c) displays quite an excellent device performance over the previous inverter without gate patterning. According to the VTCs and voltage gain curves of panels f and g of Figure 3, the high-low transition voltage was located near  $\sim -2$  V and the maximum gain (at  $V_{\rm DD}$  = 5 V) appears to be ~27, which is 4.5 times higher than that of CMOS with a universal gate. Figure 3h dispalys sub-nanowatt power consumption behavior in the static states, which is one of the intrinsic advantages from a complementary inverter. In particular, the peak power was as small as 10 nW but would be less than sub-nanowatt<sup>35,39</sup> during dynamic inverter switching in a small input voltage range (for instance, between -3 and 0 V). We attribute such a small power consumption to the gate patterning, low supply voltage  $(V_{

m DD})$ , and FET device isolation as a result of the hetero-2D CMOS structure. Dynamic switching was carried out at 500 Hz, as shown in Figure 3i; here, we used  $V_{\rm IN}$  between -5 and 0 V under a  $V_{\rm DD}$  of 2 V. No over-/undershoot phenomena were

shown, because the overlap capacitance was much reduced by gate patterning unlike the case of the other device with a universal gate. A dynamic switching delay of  $\sim 800~\mu s$  was observed for 2 V full output signal, somewhat attributed to the overlap capacitance. In fact, it might not be easy to obtain high-quality WSe<sub>2</sub> and MoS<sub>2</sub> nanosheets on Al<sub>2</sub>O<sub>3</sub>/patterned gate (Au/Ti), which causes the nanosheets to be warped unlike the cases on the flat SiO<sub>2</sub>/p<sup>+</sup>-Si gate. However, according to AFM results in Figure S4, the surface contour of the patterned Au/Ti electrode structure appears quite safe, showing a very small aspect ratio ( $\sim 0.03$ ). Because ALD Al<sub>2</sub>O<sub>3</sub> should be conformal on the Au/Ti electrode, the roughness and contour of ALD Al<sub>2</sub>O<sub>3</sub> gate dielectric would be almost the same as that of Au/Ti. As a result, our FETs appear working well without any problem.

Hetero-CMOS Modulated Using Thin 2D Nanosheets and CYTOP Layer. Despite the above operation of hetero-CMOS inverter on glass, the device may not be practical yet in terms of logic function, because the device shows negative

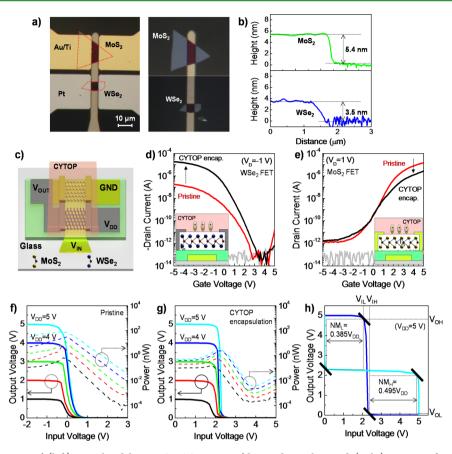

Figure 4. (a) Optical images of (left) completed hetero-CMOS inverter fabricated on glass and (right) just transferred n-MoS<sub>2</sub> and p-WSe<sub>2</sub> nanosheets onto Al<sub>2</sub>O<sub>3</sub> gate-insulator/patterned gate. (b) AFM line profiles of 5.4 nm thin MoS<sub>2</sub> and 3.5 nm thin WSe<sub>2</sub> nanosheets. (c) Schematic 3D illustration of hetero-CMOS inverter encapsulated with a fluoropolymer CYTOP layer on top.  $I_D$ – $V_{GS}$  transfer curves of patterned bottom-gate FETs for (d) p-channel WSe<sub>2</sub> FET and (e) n-channel MoS<sub>2</sub> FET before and after CYTOP encapsulation. Respective insets show schematic cross-sections of CYTOP-encapsulated p- and n-FETs (see C–F bond-induced dipoles in CYTOP). Voltage transfer characteristics ( $V_{IN}$ – $V_{OUT}$ , solid line) and power consumption (dashed line) of hetero-CMOS (f) before and (g) after CYTOP encapsulation as obtained under various supply voltages ( $V_{DD}$  values) ranging from 1 to 5 V. (h) VTC and its mirror reflection of hetero-CMOS shows low and high noise margins (NM<sub>L</sub> and NM<sub>H</sub>) as obtained under  $V_{DD}$  = 5 V.

transition voltage (-2 V); it remains as a serious problem resulting in V<sub>IN</sub>-V<sub>OUT</sub> signal mismatch in NOT gate, invalidating any logic function. This originates from the fact that our two FETs are in depletion mode. To resolve this issue of  $V_{\rm IN}-V_{\rm OUT}$  signal mismatch, we attempted to fabricate another set of glass-substrate hetero-CMOS (Figure 4a) using little thinner p-WSe<sub>2</sub> and n-MoS<sub>2</sub> flakes (3.5 and 5.4 nm, respectively, in Figure 4b) for the channel along with a CYTOP passivation layer coating on CMOS devices (Figure 4c), in consideration that our back-gate FETs with thin flake channels may have a smaller number of carriers, which induce a threshold voltage shift in FETs. 13 Moreover, the organic CYTOP contains C-F bond-induced dipoles inside (see the dipole schemes in the inset FETs of panels d and e of Figure 4), which are supposed to induce more holes into thin p-WSe<sub>2</sub> and to reduce electrons in thin n-MoS2, controlling their respective I<sub>D</sub> current.<sup>24</sup> In addition, the device needs a top passivation layer anyway for ambient stability improvement. As a consequence, we could control the ID current in p- and n-FETs, as shown in panels d and e of Figure 4; the 3.5 nm thin p-WSe<sub>2</sub> channel initially shows 0.2  $\mu$ A ( $\mu_{\rm sat}$  = 0.1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at  $V_{\rm D}$  = -1 V, and  $\mu_{\rm lin} \sim 20$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at -0.1 V) but later 10  $\mu$ A ( $\mu_{\rm sat}$  = 17 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and  $\mu_{\rm lin} \sim 40$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) with a threshold voltage of ~0.5 V (as shown in Figure S5d) after CYTOP passivation, and in the opposite way, the 5.4 nm thin

n-MoS $_2$  channel displays initial 20  $\mu$ A ( $\mu_{lin}$  = 22 cm $^2$  V $^{-1}$  s $^{-1}$ ) and final 2  $\mu$ A ( $\mu_{lin}$  = 7 cm $^2$  V $^{-1}$  s $^{-1}$ ) with a threshold voltage  $(V_{\rm TH} \sim 2.9 \text{ V, as shown in Figure S5e})$  of an enhanced mode FET. Such thickness effects almost realize a positive transition voltage (~0.1 V) in our CMOS VTC curves of Figure 4f, but peak power consumption and voltage gain degrade somehow to be 100 nW and ~10, respectively. Noticeable improvement in the VTC behavior of the CMOS inverter actually came from CYTOP encapsulation, as shown in Figure 4g; positive transition voltage of 2.3 V (at 3-5 V of  $V_{\rm DD}$ ) was achieved along with a high voltage gain of 23 and ~1 nW peak power consumption. Moreover, an almost ideal noise margin<sup>39</sup> was obtained for much improved signal matching, as seen in Figure 4h, where  $NM_L = 0.385V_{DD}$  and  $NM_H = 0.495V_{DD}$ . We again attribute this type of success to the thickness modulation and CYTOP encapsulation, which could control the threshold voltage and  $I_D$  current as well, because we could finally achieve the enhanced mode n-MoS2 FET without losing the mobility (or on-current  $I_D$ ) value of WSe<sub>2</sub> and MoS<sub>2</sub> FETs. More details on the mobility plots and voltage gain curves are found in panels a-c and f-h of Figure S5, respectively. As a matter of fact, in typical complementary inverters, the transition voltage appears apparently proportional to the supply voltage  $(V_{DD})$ because p- and n-channel FETs show quite a symmetrical behavior in output and transfer characteristics. Therefore, most

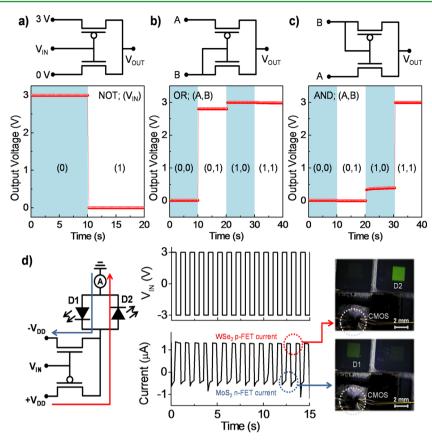

Figure 5. Schematic circuit diagrams and time domain  $V_{\rm OUT}$  versus  $V_{\rm IN}$  plots of (a) NOT, (b) OR, and (c) AND logic gates. Input logic (0) and (1) indicate the input voltages of 0 and 3 V, respectively. (d) Left circuit diagram describes a push—pull circuit comprised of hetero-CMOS inverter and two antiparallel OLEDs. Central plots show input voltage and output current curves at 10 Hz switching. Right snapshot images display the alternative switching of green OLEDs (D1 and D2) by n-MoS<sub>2</sub> and p-WSe<sub>2</sub> FETs.

ideal transition voltage would be  $0.5V_{\rm DD}$  according to load-line analysis. However, our case is quite deviated from ideal symmetry; the p-type WSe<sub>2</sub> transistor approaches to saturation behavior and shows ~10 times higher mobility than that of our n-type MoS<sub>2</sub> transistor with linear output behavior. As a result, our inverter might behave as somewhat resistive-load (or depletion-load) type, which also shows proportionality but with a small increase of transition voltage, despite a large  $V_{\rm DD}$  increase,  $^{35,40,41}_{35,40,41}$  although our complementary-like inverter brought good power consumption and noise margin.

Logic Gates and Push-Pull Circuit Based on 2D Hetero-CMOS. On the basis of the above hetero-CMOS inverter with a positive transition voltage, two types of applications were implemented: basic logic operation (using pass transistor circuits)<sup>42</sup> and OLED switching. According to the respective plots of panels a, b, and c of Figure 5 for NOT, OR, and AND logics in the pass transistor circuits, 42 our hetero-CMOS circuits appear nicely operating when 0 and 3 V input voltages  $(V_{IN})$  were applied for central, A, and B terminals (for NOT gate,  $V_{\rm DD}$  = 3 V). More interesting may be the push-pull circuit of Figure 5d to alternatively switch two OLED pixels (D1 and D2). The alternative  $V_{\rm DD}$  values of -3and +3 V were dynamically supplied with 1-10 Hz square wave  $V_{\rm IN}$  of  $\pm 3$  V. Because the WSe<sub>2</sub> p-FET could supply a higher current as expected from Figure 4d, the corresponding OLED pixel (D2) appears brighter than the other pixel (D1), which is switched on by MoS<sub>2</sub> n-FET. For more details, 1, 5, and 10 Hz switching operations are demonstrated in a supporting AVI file (supporting video clip), while the device property of green

OLEDs (courtesy of Samsung Display) is also shown as I-V curves in Figure S6 for reference.

#### CONCLUSION

In summary, hetero-CMOS inverters with 2D semiconductor channel FETs of p-WSe2 and n-MoS2 have been successfully fabricated on both 285 nm thick SiO<sub>2</sub>/p<sup>+</sup>-Si and glass substrates using a direct imprinting method. Our hetero-CMOS inverters with bottom-gated p- and n-FETs well operate on both substrates, but they show much superior performances on glass because of gate patterning, electrical isolation between n- and p-FETs, and much reduced overlap capacitance: faster dynamic switching behavior, higher voltage gain of ~27, and subnanowatt power consumption. Input-output signal mismatch, caused by negative transition voltage in the CMOS device, was resolved using thinner flake channels and CYTOP encapsulation, which result in both enhanced mode n-FET and a positive CMOS transition voltage. Our CMOS device with a patterned gate on a glass substrate well operates in the circuits of NOT, OR, and AND logic, also demonstrating a push-pull circuit for OLED pixel switching. We now conclude that our 2D hetero-CMOS inverter by a simple direct imprint method is quite useful and promising toward future nanodevice/electronic applications.

## ASSOCIATED CONTENT

#### S Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsami.5b06027.

Table for published reports on 2D-CMOS, schematic images describing fabrication processes, gate voltage versus mobility plots, square root drain current versus gate voltage ( $\sqrt{I_{\rm D}}-V_{\rm GS}$ ), and drain current versus gate voltage ( $I_{\rm D}-V_{\rm GS}$ ) plots to obtain threshold voltages, drain current—drain voltage ( $I_{\rm D}-V_{\rm DS}$ ) output curves, AFM result of the patterned Au/Ti gate on glass, voltage gain ( $-{\rm d}V_{\rm OUT}/{\rm d}V_{\rm IN}$ ) plots of hetero-CMOS as a function of the input voltage, and current—voltage (I-V) curves of green OLED (PDF) Supporting video clip (AVI)

#### AUTHOR INFORMATION

### **Corresponding Author**

\*Telephone: 82-2-2123-2842. Fax: 82-2-392-1592. E-mail: semicon@yonsei.ac.kr.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors acknowledge the financial support from the National Research Foundation of Korea (NRF) (NRL Program, Grant 2014R1A2A1A01004815; Nano-Materials Technology Development Program, Grant 2012M3A7B4034985), the Yonsei University (Future-Leading Research Initiative of 2014, Grant 2014-22-0168), and the Brain Korea 21 Plus Program.

#### REFERENCES

- (1) Geim, A. K. Graphene: Status and Prospects. Science 2009, 324, 1530-1434.

- (2) Novoselov, K. S.; Jiang, D.; Schedin, F.; Booth, T. J.; Khotkevich, V. V.; Morozov, S. V.; Geim, A. K. Two-Dimensional Atomic Crystals. *Proc. Natl. Acad. Sci. U. S. A.* **2005**, *102*, 10451–10453.

- (3) Jariwala, D.; Sangwan, V. K.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Emerging Device Applications for Semiconducting Two-Dimensional Transition Metal Dichalcogenides. *ACS Nano* **2014**, *8*, 1102–1120.

- (4) Wang, Q. H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Electronics and Optoelectronics of Two-Dimensional Transition Metal Dichalcogenides. *Nat. Nanotechnol.* **2012**, *7*, 699–712.

- (5) Lee, S.; Zhong, Z. Nanoelectronic Circuits Based on Two-Dimensional Atomic Layer Crystals. *Nanoscale* **2014**, *6*, 13283–13300.

- (6) Coleman, J. N.; Lotya, M.; O'Neill, A.; Bergin, S. D.; King, P. J.; Khan, U.; Young, K.; Gaucher, A.; De, S.; Smith, R. J.; Shvets, I. V.; Arora, S. K.; Stanton, G.; Kim, H.-Y.; Lee, K.; Kim, G. T.; Duesberg, G. S.; Hallam, T.; Boland, J. J.; Wang, J. J.; Donegan, J. F.; Grunlan, J. C.; Moriarty, G.; Shmeliov, A.; Nicholls, R. J.; Perkins, J. M.; Grieveson, E. M.; Theuwissen, K.; McComb, D. W.; Nellist, P. D.; Nicolosi, V. Two-Dimensional Nanosheets Produced by Liquid Exfoliation of Layered Materials. *Science* 2011, 331, 568–571.

- (7) Song, H. S.; Li, S. L.; Gao, L.; Xu, Y.; Ueno, K.; Tang, J.; Cheng, Y. B.; Tsukagoshi, K. High-Performance Top-Gated Monolayer SnS2 Field-Effect Transistors and Their Integrated Logic Circuits. *Nanoscale* **2013**, *5*, 9666–9670.

- (8) Lin, Y.-F.; Xu, Y.; Wang, S.-T.; Li, S.-L.; Yamamoto, M.; Aparecido-Ferreira, A.; Li, W.; Sun, H.; Nakaharai, S.; Jian, W.-B.; Ueno, K.; Tsukagoshi, K. Ambipolar MoTe<sub>2</sub> Transistors and Their Applications in Logic Circuits. *Adv. Mater.* **2014**, *26*, 3263–3269.

- (9) Yu, L.; Lee, Y.-H.; Ling, X.; Santos, E. J. G.; Shin, Y. C.; Lin, Y.; Dubey, M.; Kaxiras, E.; Kong, J.; Wang, H.; Palacios, T. Graphene/MoS<sub>2</sub> Hybrid Technology for Large-Scale Two-Dimensional Electronics. *Nano Lett.* **2014**, *14*, 3055–3063.

- (10) Cheng, R.; Jiang, S.; Chen, Y.; Liu, Y.; Weiss, N.; Cheng, H.-C.; Wu, H.; Huang, Y.; Duan, X. Few-Layer Molybdenum Disulfide

- Transistors and Circuits for High-Speed Flexible Electronics. *Nat. Commun.* **2014**, *5*, 5143.

- (11) Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M. L.; Li, L.-J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. *Nano Lett.* **2012**, *12*, 4674–4680.

- (12) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

- (13) Lee, H. S.; Min, S.-W.; Chang, Y.-G.; Park, M. K.; Nam, T.; Kim, H.; Kim, J. H.; Ryu, S.; Im, S. MoS<sub>2</sub> Nanosheet Phototransistors with Thickness-Modulated Optical Energy Gap. *Nano Lett.* **2012**, *12*, 3695–3700.

- (14) Roy, T.; Tosun, M.; Kang, J. S.; Sachid, A. B.; Desai, S. B.; Hettick, M.; Hu, C. C.; Javey, A. Field-Effect Transistors Built from All Two-Dimensional Material Components. *ACS Nano* **2014**, *8*, 6259–6264

- (15) Hosseini Shokouh, S. H.; Pezeshki, A.; Raza, S. R. A.; Choi, K.; Min, S.-W.; Jeon, P. J.; Lee, H. S.; Im, S. Molybdenum Disulfide Nanoflake-Zinc Oxide Nanowire Hybrid Photoinverter. *ACS Nano* **2014**, *8*, 5174–5181.

- (16) Pezeshki, A.; Hosseini Shokouh, S. H.; Raza, S. R. A.; Kim, J. S.; Min, S.-W.; Shackery, I.; Jun, S. C.; Im, S. Top and Back Gate Molybdenum Disulfide Transistors Coupled for Logic and Photo-Inverter Operation. *J. Mater. Chem. C* **2014**, *2*, 8023–8028.

- (17) Lee, Y. T.; Choi, K.; Lee, H. S.; Min, S.-W.; Jeon, P. J.; Hwang, D. K.; Choi, H. J.; Im, S. Graphene Versus Ohmic Metal as Source-Drain Electrode for MoS<sub>2</sub> Nanosheet Transistor Channel. *Small* **2014**, 10, 2356–2361.

- (18) Choi, K.; Lee, Y. T.; Min, S.-W.; Lee, H. S.; Nam, T.; Kim, H.; Im, S. Direct Imprinting of MoS<sub>2</sub> Flakes on a Patterned Gate for Nanosheet Transistors. *J. Mater. Chem. C* **2013**, *1*, 7803–7807.

- (19) Radisavljevic, B.; Whitwick, M. B.; Kis, A. Integrated Circuits and Logic Operations Based on Single-Layer MoS<sub>2</sub>. ACS Nano **2011**, 5, 9934–9938.

- (20) Huang, J.; Somu, S.; Busnaina, A. A Molybdenum Disulfide/Carbon Nanotube Heterogeneous Complementary Inverter. *Nanotechnology* **2012**, *23*, 335203.

- (21) Yu, W. J.; Li, Z.; Zhou, H.; Chen, Y.; Wang, Y.; Huang, Y.; Duan, X. Vertically Stacked Multi-Heterostructures of Layered Materials for Logic Transistors and Complementary Inverters. *Nat. Mater.* **2012**, *12*, 246–252.

- (22) Liu, H.; Neal, A. T.; Zhu, Z.; Luo, Z.; Xu, X.; Tománek, D.; Ye, P. D. Phosphorene: An Unexplored 2D Semiconductor with a High Hole Mobility. *ACS Nano* **2014**, *8*, 4033–4041.

- (23) Cho, A.-J.; Park, K. C.; Kwon, J.-Y. A High-Performance Complementary Inverter Based on Transition Metal Dichalcogenide Field-Effect Transistors. *Nanoscale Res. Lett.* **2015**, *10*, 115.

- (24) Jeon, P. J.; Min, S.-W.; Kim, J. S.; Raza, S. R. A.; Choi, K.; Lee, H. S.; Lee, Y. T.; Hwang, D. K.; Choi, H. J.; Im, S. Enhanced Device Performances of WSe<sub>2</sub>-MoS<sub>2</sub> van der Waals Junction p-n Diode by Fluoropolymer Encapsulation. *J. Mater. Chem. C* **2015**, *3*, 2751–2758.

- (25) Chuang, H.-J.; Tan, X.; Ghimire, N. J.; Perera, M. M.; Chamlagain, B.; Cheng, M. M.-C.; Yan, J.; Mandrus, D.; Tománek, D.; Zhou, Z. High Mobility WSe<sub>2</sub> p- and n-Type Field-Effect Transistors Contacted by Highly Doped Graphene for Low-Resistance Contacts. *Nano Lett.* **2014**, *14*, 3594–3601.

- (26) Das, S.; Dubey, M.; Roelofs, A. High Gain, Low Noise, Fully Complementary Logic Inverter Based on Bi-Layer WSe<sub>2</sub> Field Effect Transistors. *Appl. Phys. Lett.* **2014**, *105*, 083511.

- (27) Tosun, M.; Chuang, S.; Fang, H.; Sachid, A. B.; Hettick, M.; Lin, Y.; Zeng, Y.; Javey, A. High-Gain Inverters Based on WSe<sub>2</sub> Complementary Field-Effect Transistors. *ACS Nano* **2014**, *8*, 4948–4953.

- (28) Fang, H.; Tosun, M.; Seol, G.; Chang, T. C.; Takei, K.; Guo, J.; Javey, A. Degenerate n-Doping of Few-Layer Transition Metal Dichalcogenides by Potassium. *Nano Lett.* **2013**, *13*, 1991–1995.

- (29) Fang, H.; Chuang, S.; Chang, T. C.; Takei, K.; Takahashi, T.; Javey, A. High-Performance Single Layered WSe<sub>2</sub> p-FETs with Chemically Doped Contacts. *Nano Lett.* **2012**, *12*, 3788–3792.

- (30) Das, S.; Appenzeller, J. WSe<sub>2</sub> Field Effect Transistors with Enhanced Ambipolar Characteristics. *Appl. Phys. Lett.* **2013**, *103*, 103501.

- (31) Huang, J.-K.; Pu, J.; Hsu, C.-L.; Chiu, M.-H.; Juang, Z.-Y.; Chang, Y.-H.; Chang, W.-H.; Iwasa, Y.; Takenobu, T.; Li, L.-J. Large-Area Synthesis of Highly Crystalline WSe<sub>2</sub> Monolayers and Device Applications. ACS Nano **2014**, *8*, 923–930.

- (32) Pospischil, A.; Furchi, M. M.; Mueller, T. Solar-Energy Conversion and Light Emission in an Atomic Monolayer p-n Diode. *Nat. Nanotechnol.* **2014**, *9*, 257–261.

- (33) Baugher, B. W. H.; Churchill, H. O. H.; Yang, Y.; Jarillo-Herrero, P. Optoelectronic Devices Based on Electrically Tunable p-n Diodes in a Monolayer Dichalcogenide. *Nat. Nanotechnol.* **2014**, *9*, 262–267.

- (34) Ross, J. S.; Klement, P.; Jones, A. M.; Ghimire, N. J.; Yan, J.; Mandrus, D. G.; Taniguchi, T.; Watanabe, K.; Kitamura, K.; Yao, W.; Cobden, D. H.; Xu, X. Electrically Tunable Excitonic Light-Emitting Diodes Based on Monolayer WSe<sub>2</sub> p-n Junctions. *Nat. Nanotechnol.* **2014**, *9*, 268–272.

- (35) Shokouh, S. H. H.; Pezeshki, A.; Ali Raza, S. R.; Lee, H. S.; Min, S.-W.; Jeon, P. J.; Shin, J. M.; Im, S. High-Gain Subnanowatt Power Consumption Hybrid Complementary Logic Inverter with WSe<sub>2</sub> Nanosheet and ZnO Nanowire Transistors on Glass. *Adv. Mater.* **2015**, 27, 150–156.

- (36) Muller, R. S.; Kamin, T. I.; Chan, M. Device Electronics for Integrated Circuits, 3rd ed.; John Wiley & Sons: New York, 2003; p 431.

- (37) Fuhrer, M. S.; Hone, J. Measurement of Mobility in Dual-Gated MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2013**, *8*, 146–147.

- (38) Oh, M. S.; Choi, W.; Lee, K.; Hwang, D. K.; Im, S. Flexible High Gain Complementary Inverter Using n-ZnO and p-Pentacene Channels on Polyethersulfone Substrate. *Appl. Phys. Lett.* **2008**, *93*, 033510.

- (39) Dey, A. W.; Svensson, J.; Borg, B. M.; Ek, M.; Wernersson, L.-E. Single InAs/GaSb Nanowire Low-Power CMOS Inverter. *Nano Lett.* **2012**, *12*, 5593–5597.

- (40) Dai, Y.; Wu, P.; Dai, L.; Fang, X.; Qin, G. Hybrid Complementary Metal-Oxide-Semiconductor Inverters Based on Single Nanowires. *J. Mater. Chem.* **2011**, 21, 2858–2862.

- (41) Gao, P.; Zhang, Q. Encapsulate-and-Peel: Fabricating Carbon Nanotube CMOS Integrated Circuits in a Flexible Ultra-Thin Plastic Film. *Nanotechnology* **2014**, *25*, 065301.

- (42) Ding, L.; Zhang, Z.; Liang, S.; Pei, T.; Wang, S.; Li, Y.; Zhou, W.; Liu, J.; Peng, L.-M. CMOS-Based Carbon Nanotube Pass-Transistor Logic Integrated Circuits. *Nat. Commun.* **2012**, *3*, 677.